Since: 14,Octorber 2004 : Revision 2, September 2025

Trans Linear Bias AMP3 01

TLB AMP2は、TLB AMP1より音質改善できました。しかし、深く考えずにPCBを作画したため110 X 45 mmで、格安PCBの対応外で高コスト、トランス整流方式の筐体(タカチOS133-26-24)は天板が締まらず納まりません。 100 X 45 mm以下のサイズでTLB AMP3を計画しました。TLB AMP2のPCBを小さくするだけではなく、TLB AMP1の音質改善をすることにします。また、電圧ブースタ加わりオープンループ利得が高く位相補正が難しくなりました。ADA4700^1にJFET初段を加え、初段を定電圧化し性能音質改善を置きなうことにしました。

これまで2台製作し、開ループ利得が異なるのに、同じような歪率特性でした。 この原因の一つには、Current Mirror回路の二つのトランジスタは同じ特性でなければなりませんが、ディスクリートで完全に揃っているとは言い切れません。

片方のトランジスタをハンダ鏝で加熱すると面白いようにTHDが変化します。二つのトランジスタは同一のサブストレート上に構成されている必要があります。1970~80年代にはDual Transistorが幾つも販売されていましたが、今では全く見かけません。with3motorさんに相談したところ、BCV61とBCV61を探してくれました。Dual Transistorだけでなく、Current Mirror用の素子で目的に合致します。

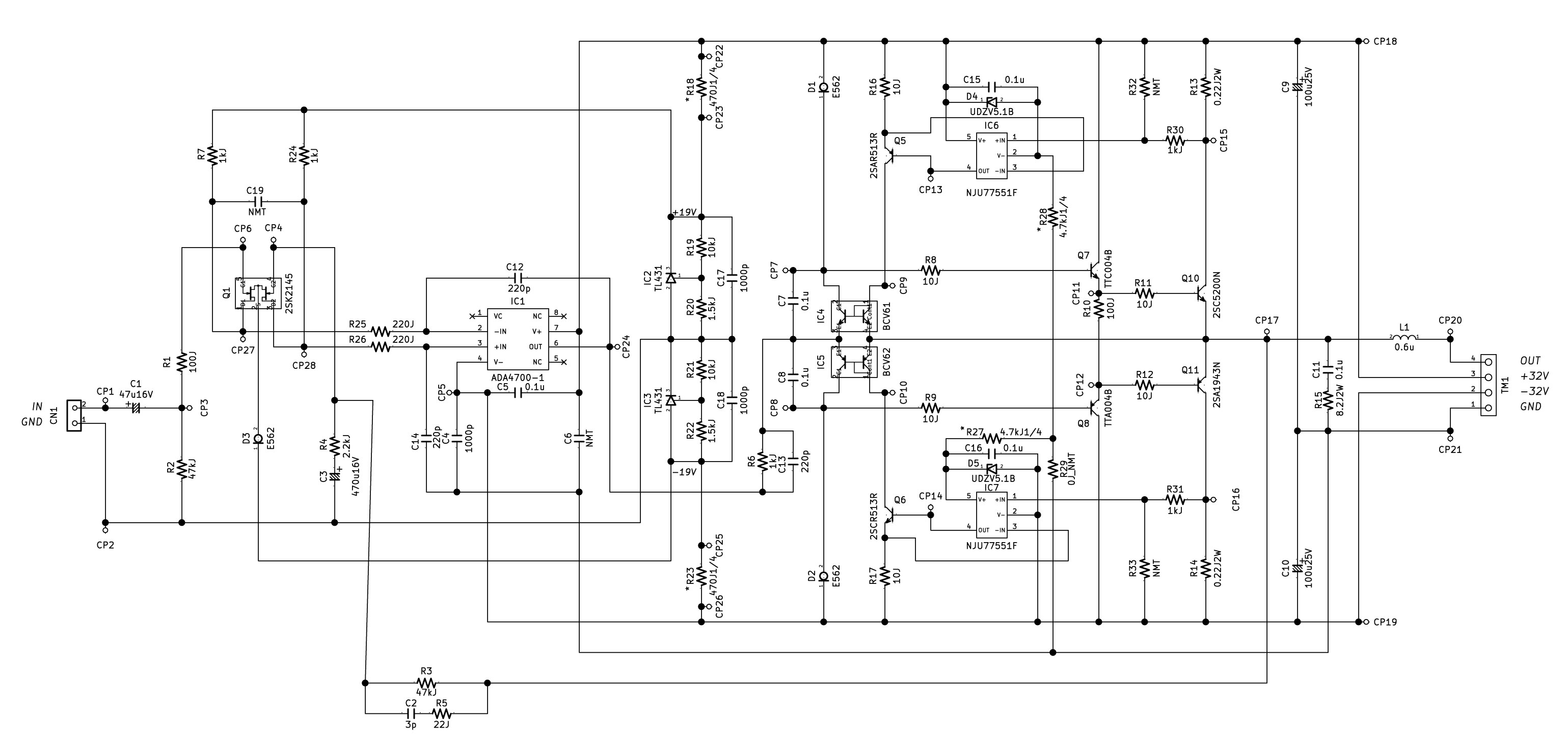

終段の電流を検出して帰還させるCurrent Mirrorは、大電力トランジスタと小電力トランジスタの構成でどう考えても特性が異なります。そこでトランジスタによる検出をやめ、定電流回路に置き換えることにします。

TLB 2を試聴し、初段をシャントレギュレータTL431で定電圧化による改善を確認しました。TLB 2は、OP Amp + 電圧ブースタ構成としましたが、今回はADA4700-1にシャントレギュレータTL431で定電圧化したFET差動アンプ(幸いDual J-FET 2SK2145を入手できました)を初段に用い開ループ利得を上げてNFBが深くかかるようにします。終段からの定電流回路はNJU77551を±24VからUDZV5.1で駆動します。

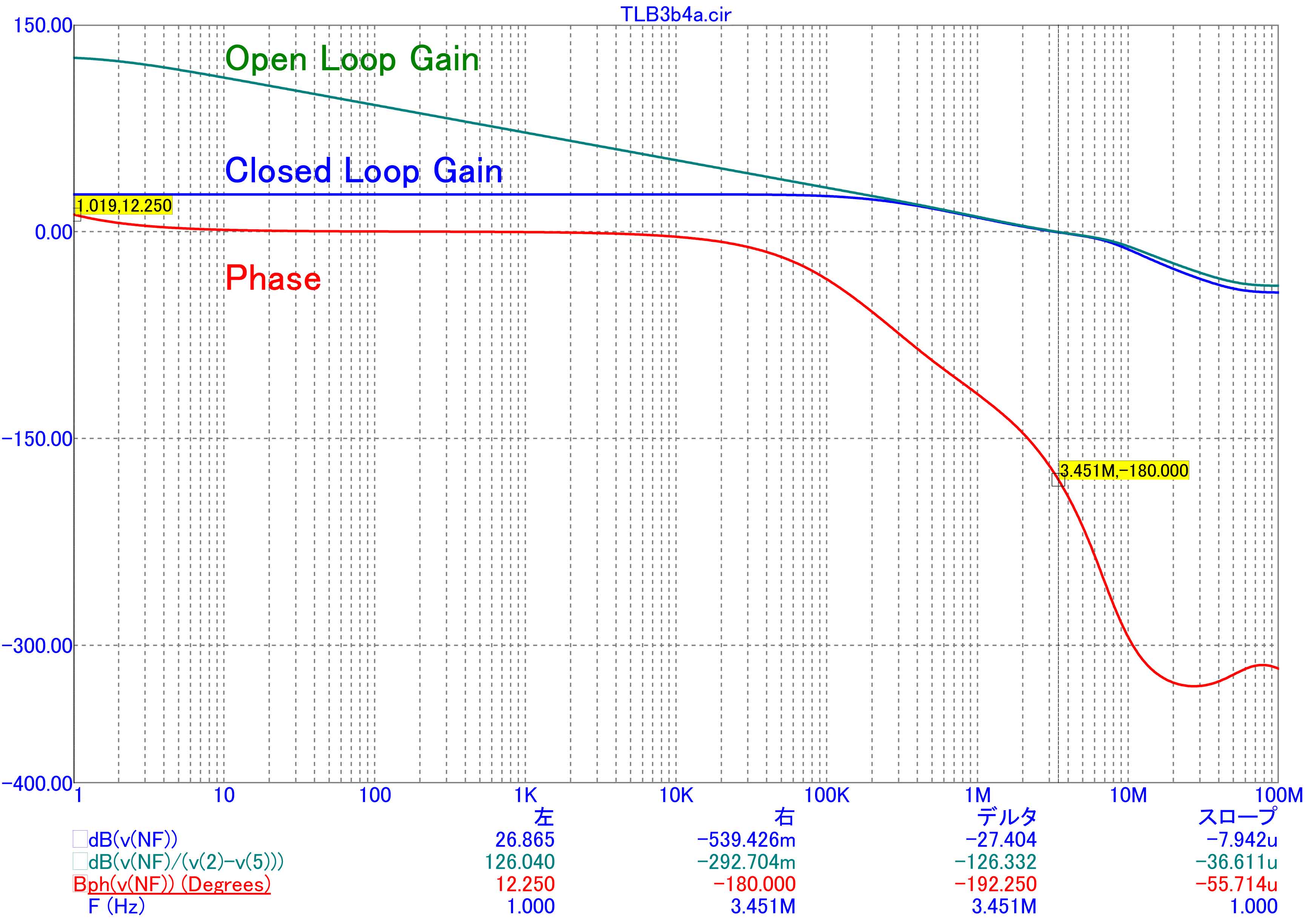

シミュレーションの結果は

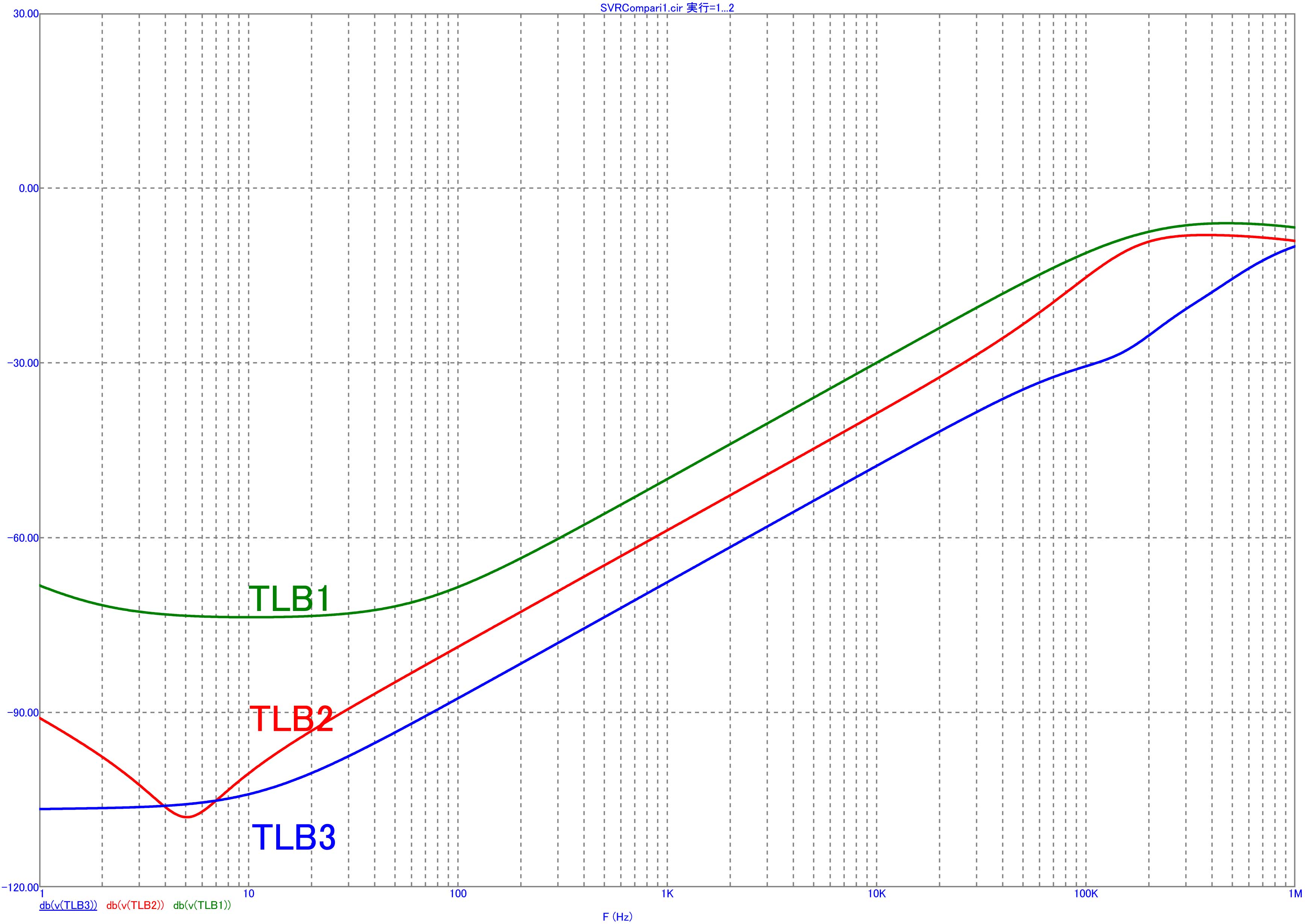

開ループ利得127.4dB、位相余裕-0.54dBとなります。追加した2SK2145初段は16dBほどの利得です。TLB 1は、ADA4700-1の利得だけで、開ループ利得109.8dB、TLB 2は、NE5532+電圧ブースタ構成で、開ループ利得は135.8dBあり、位相補正に苦労した割に高域の特性に不満が残りました。今回はそれらの中間の利得に収めました。

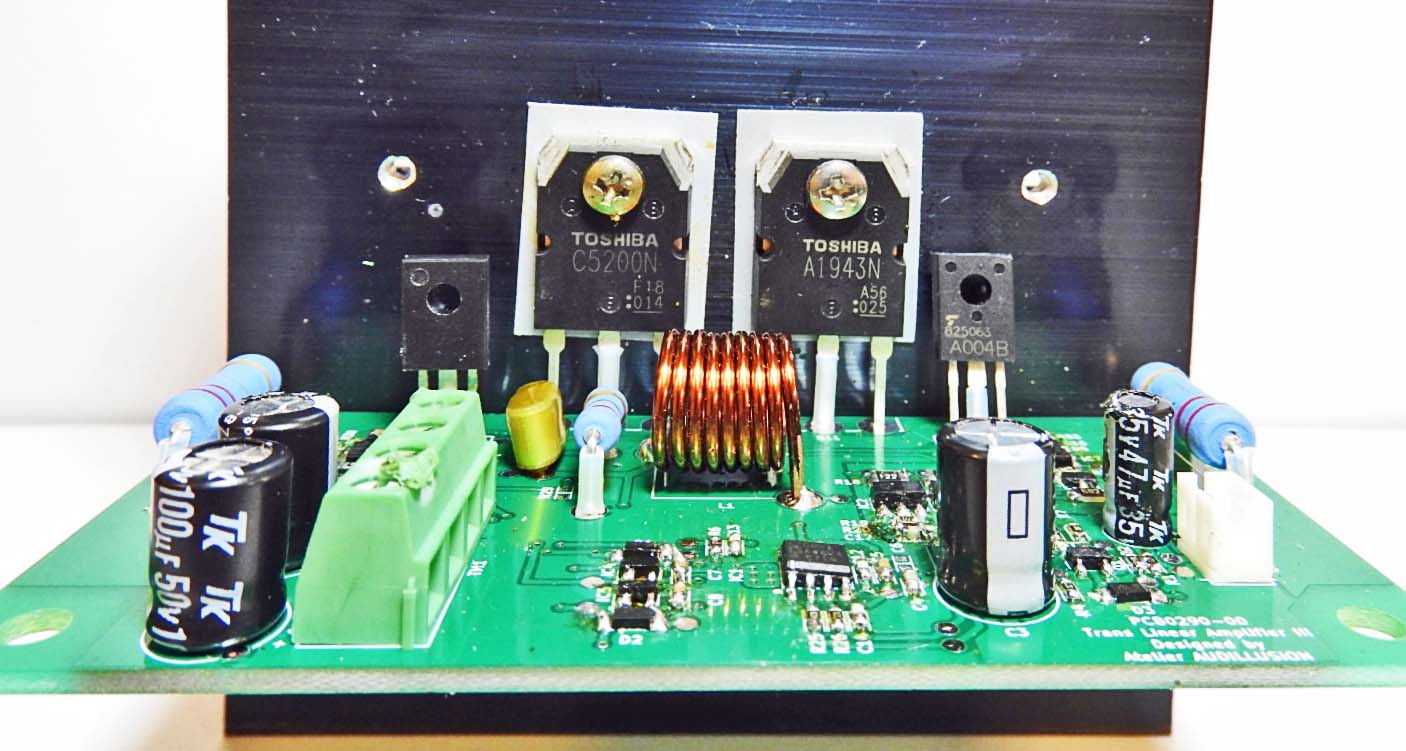

PCBは、トランス整流式の筐体への実装を考慮して98 X 45 mmとしました。

![]()

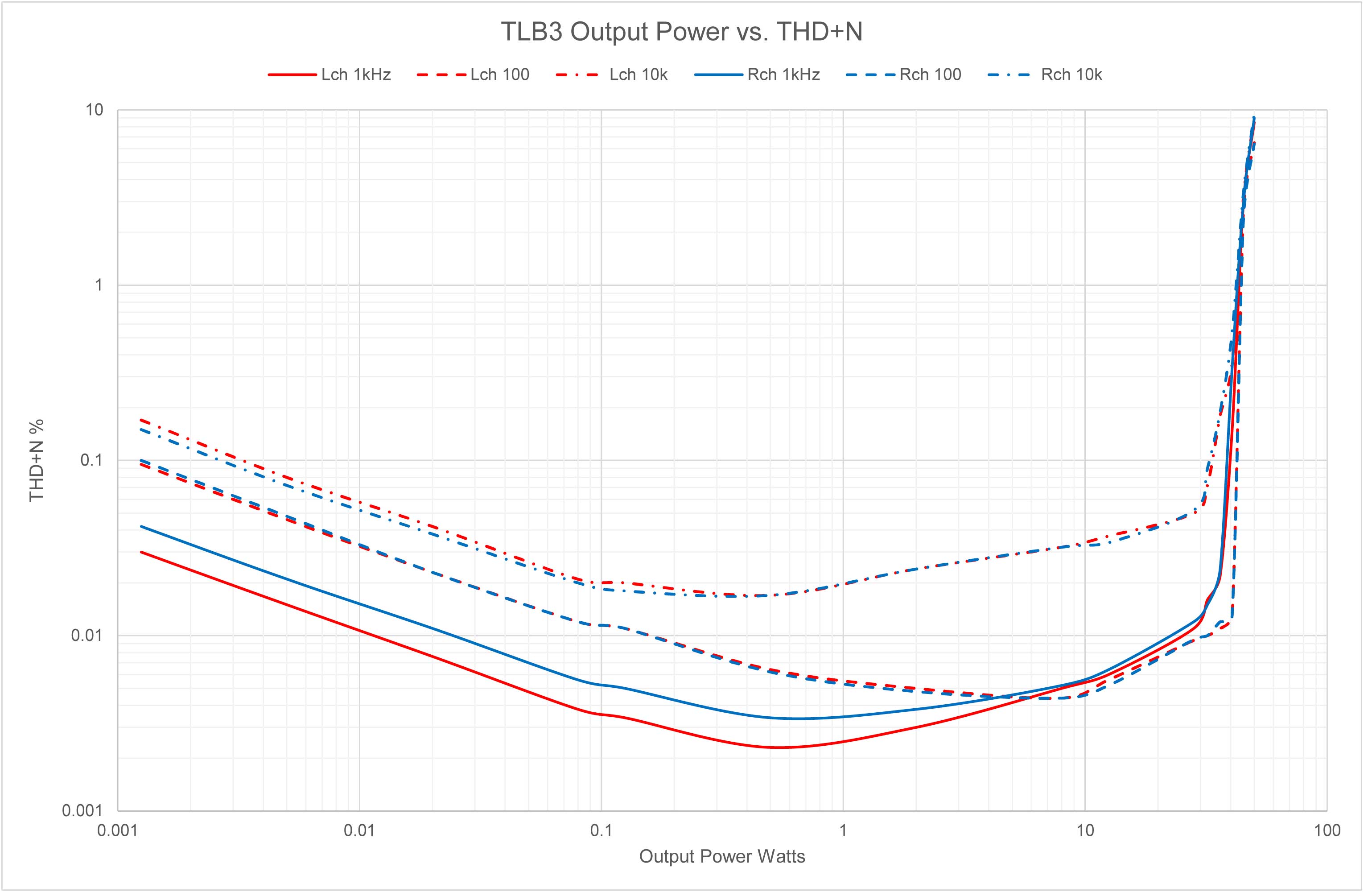

放熱器幅100mmなので、トランス整流方式の筐体(タカチOS133-26-24)にも収まります。AC24Vトランス・整流電源、負荷抵抗8Ω、歪率特性は、1kHz0.003%以下、10kHz0.02%以下となりました。

8watts時の歪の出方は、

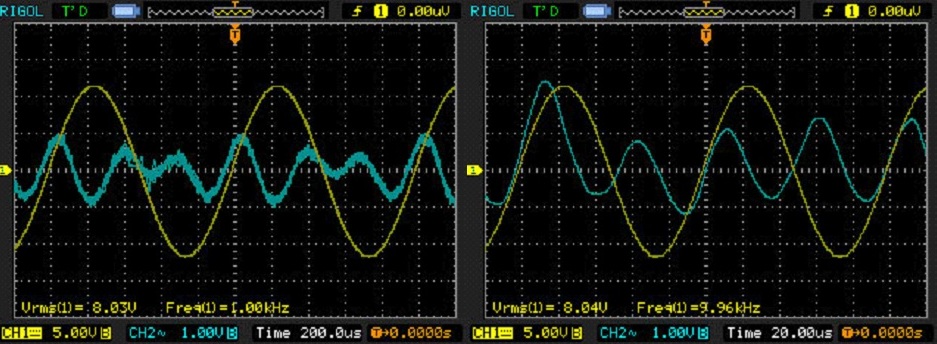

1kHz, 10kHz

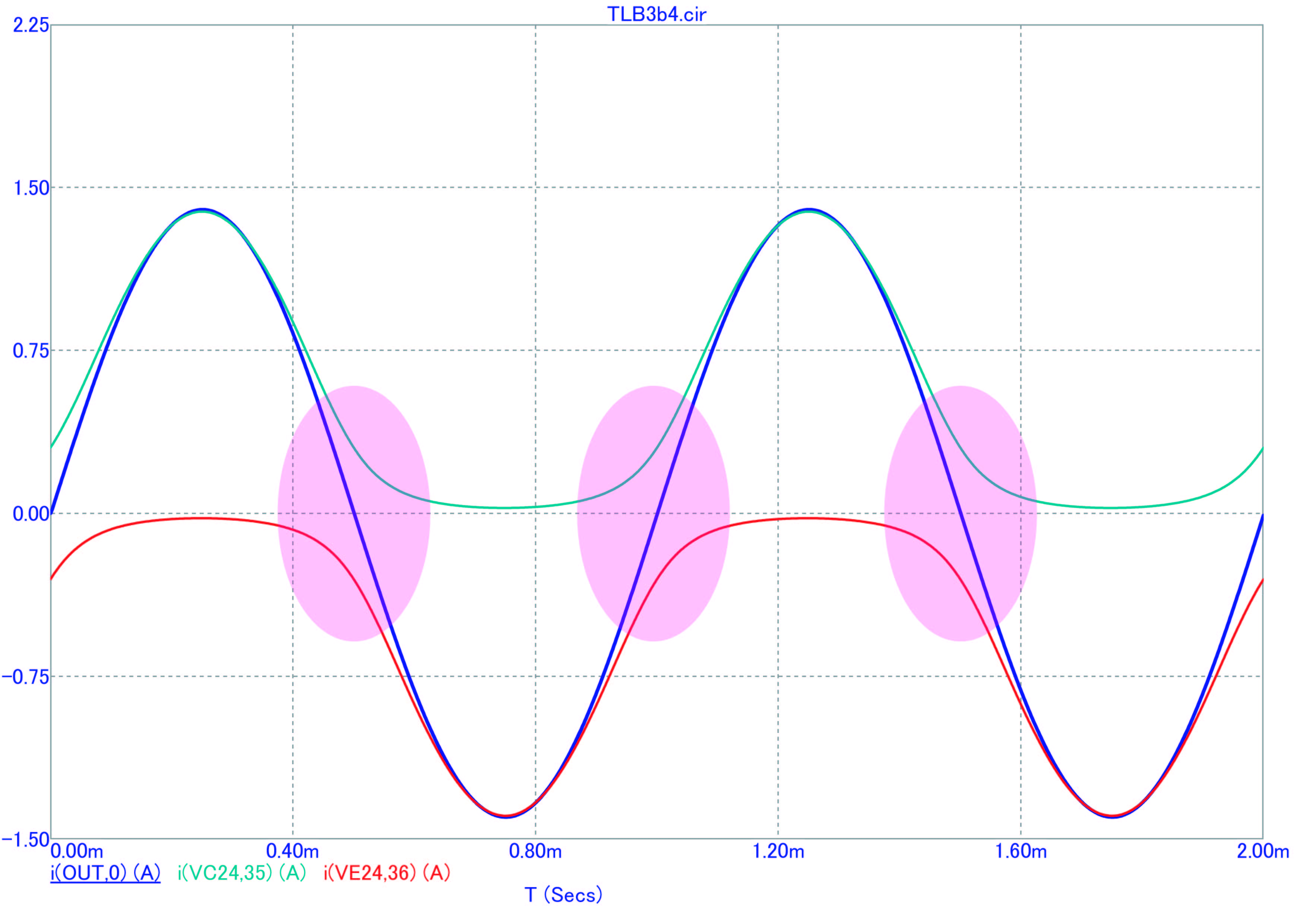

Trans Linear Bias AMP1、2より低歪率を目論みCurrent Mirror ICと定電流回路でTrans Linearを構成し、それなりの効果が得られ、20~20kHzで0.1%以下となりました。 一般的なBiasAMPより、残念ながら歪は大きいといえます。この原因を推測します。室力8watts、1kHzで、負荷抵抗8Ω、終段NPNとPNPトランジスタに流れる電流をシミュレーションします。

終段トランジスタに流れる電流はカットオフすることなくTrans Linear Biasの特徴です。 受け渡しの赤丸部分はNPN、PNPトランジスタの特性そのもので、一見上手くいっているように見えていますが同一の特性ではありません。この部分で歪が増えます。信号の周波数が低ければこの部分の割合が小さく、歪率も低くなります。信号周波数が高いと周期が短くこの部分の割合が大きくなり、歪率も大きくなります。終段トランジスタを何種類かシミュレーションしましたが、傾向は同じで大差ありませんでした。 これ以上の低歪率化は今後の課題です。

音質

緑TLB AMP1, 1kHz: -50dB、赤TLB AMP2, 1kHz: -59dB、青TLB AMP3, 1kHz: -68dBと改善されています。トランス整流電源は非定電圧電源で、SVRRの影響を大きく受けるので、定電圧電源のスイッチング電源との聴感の違いが大きくなります。